Efficient state identification for finite state machine-based testing

Uraz Cengiz Türker Member, IEEE, Robert M. Hierons, Mohammad Reza Mousavi, and Khaled El-Fakih

Abstract—The practice of testing software systems modelled as Finite State Machines (FSMs) has garnered significant attention owing to its simplicity. In FSM-based testing, the tester derives a test suite from the FSM model representing the system's specification. Subsequently, this test suite is executed against the implementation, and the tester uses the output to decide whether the implementation conforms to the specification. Often, a test suite generation technique requires input sequences to check whether the FSM is in the intended state. This task is referred to as state identification and is often carried out using a set of input sequences called a characterising set. Even though the use of characterising sets simplifies testing, they require a reliable reset or reset sequence and additional transfer sequences. Unfortunately, resetting the underlying system can be costly or may entail manual configuration. In addition, transfer sequences do not directly contribute to testing. This work introduces a class of characterising sets (Ordered Characterising Sets (O-WSets)) that avoid using resets or transfers by design. We show that checking the existence of such a characterising set is NPcomplete. We introduce the notion of bounded O-WSets (BO-WSets), which are types of O-WSets that limit transfer usage, and give an algorithm that constructs these. In experiments, on average, the proposed approach led to reductions in the number of resets (95% for real FSMs; 99.73% for synthetic FSMs), the number of transfer inputs (53% for real FSMs; 63.3% for synthetic FSMs) and the number of inputs in state identification sequences (50% for real FSMs; 66.6% for synthetic FSMs). Additionally, the proposed algorithm reduced the time and memory required to derive state identification sequences by 85% and 23%, respectively. Finally, the approach led to test suites with 49.3% fewer sequences and 33.3% fewer inputs on average.

Index Terms—State identification, finite state machines, software engineering/ software/program verification, software engineering/test design, software engineering/testing and debugging.

#### I. Introduction

TESTING is a costly but indispensable part of software development [1]. Manual configuration and test case design comprise a large portion of this cost. Automating software testing is the most promising pathway to reducing this cost, and model-based testing (MBT) has been shown to be an efficient test automation method. In MBT, when the underlying system can be represented using finitely many states and transitions between them, the model is typically an abstract machine, such as a Finite State Machine (FSM) [2],

U.C. Türker was with the School of Computing and Communications, Lancaster University, Lancaster, UK, LA1 4YW. E-mail: u.turker@lancaster.ac.uk Robert M Hierons was with the School of Computer Science, The University of Sheffield, Sheffield, UK.

Mohammad Reza Mousavi was with the Department of Informatics, Kings College London, UK.

Khaled El-Fakih was with the Department of Computer Science and Engineering, American University of Sharjah, UAE.

Extended FSM [3], or a timed FSM [4]. Such models are often converted into FSMs for test derivation.

The term FSM is an umbrella term, and based on the underlying system, an FSM can be complete/partial and deterministic/non-deterministic. This work concerns test derivation for an important class of FSMs: FSMs that are complete and deterministic. We use the term FSM for such FSMs. FSM-based testing provides a rigorous discipline for functional (conformance) testing of communication protocols [5]–[10], sequential circuits [2], [11]–[14], parsers and compilers [15], software design [5], object-oriented systems [16], embedded components [17], and web services [18]–[21].

A multitude of FSM-based testing techniques have been proposed [2], [5], [9], [11], [12], [22]–[37] based on the concept of a *fault detection experiment* originally introduced for sequential circuits and switching systems [2], [11], [12], [14]. Such techniques have been shown to be effective when used in significant industrial projects [38].

FSM-based testing techniques derive a test suite T from the specification FSM M. Such a test suite is a set of test cases, where each test case has an input sequence and the corresponding expected output sequence. Testing then involves applying the input sequences in the test cases from T to the implementation under test (IUT) N and checking that the expected output sequences are produced by N. FSM-based test generation techniques are appealing because they can be automated and, in addition, some such techniques produce a finite test suite such that, if certain well-defined assumptions hold, every faulty IUT N of the specification M is guaranteed to fail the test suite.

In FSM-based testing, the size of the test suite (the total number of inputs and the total number of input sequences) and the time required to derive the test suite are important as they affect the cost of testing. Naturally, techniques that can derive reduced-cost test suites are preferred, and developing such techniques is an active research area [39], [40].

Many FSM-based test generation techniques utilise sequences to i) identify the states and ii) verify the transitions of the  $IUT\ N\ [5]$ , [27], [41]. State identification, for a state s of M, is usually achieved through a set W containing one or more input sequences (state-identification sequences). Here, for every other state  $s' \neq s$  of M, W must contain an input sequence w that separates s and s': different output sequences are produced by applying w in states s and s'. A set of state-identification sequences can then be used to check that N is in the expected state s: One separately applies the input sequences from W to N (in the current state) and observes the output sequences produced by N. If N produces the expected

1

output sequences, we say that s is identified in N. To verify whether N correctly implements a transition of M, we reset N, bring it to the starting state of the transition, apply the transition's input, observe the output produced by N, and then identify its ending state using state-identification sequences. If N produces the expected outputs, then the transition is *verified*.

If all the states are identified and all the transitions are verified, then we know that N is a (conforming) implementation. If, during testing, N produces an unexpected output sequence, then we know that N is a faulty implementation. As a result of their role in state identification and transition verification, the size of and the time required to derive state identification sequences affect the cost of testing [7], [42].

Several types of state-identification sequences have been proposed. The most commonly used are Distinguishing sequences (DSs) [11], [14], Unique Input-Output sequences (UIOs), and characterising sets (W-Sets). Both DSs and UIOs use only one sequence to identify a state s of M, making it easier to identify a state of the IUT. However, not all FSMs have UIOs or DSs. Checking the existence of a DS or UIOs is PSPACE-complete [23], although there are classes of FSMs for which these problems can be solved in polynomial time [43].

In contrast, every completely specified minimal FSM M has a W-set: a state identification set that can contain more than one input sequence. In addition, a W-set can be found in time that is polynomial with respect to the size of M [5] and, if M has n states, there is always such a W-set that contains at most n-1 input sequences, all of length at most n-1 [11]. Therefore, W-Sets are often preferred. W-Sets are employed by the prominent W [5], Wp [27], H [30], and HSI [41] test suite derivation methods and have been used in many other test generation techniques (see, for example, [41], [44]). Furthermore, W-Sets are also utilised in automated model learning [45] where the W-Method is used to decide whether a given hypothesis (FSM) is conforming [46]–[53]. The W-method is a systematic test generation technique with guaranteed fault detection and many industrial software testing systems (such as X-Machine Testing [54]) and machine inference tools (such as LearnLib [55]-[57], and AalPy [58]) use the W-method. Note, however, that there are FSM-based test generation algorithms that utilise other approaches to state identification (see, for example, [35], [59], [60]).

Unfortunately, the use of W-Sets introduces additional costs into testing due to resets and transfer sequences. Specifically, to identify a state or verify a transition of N, for every sequence w in the W-Set, we bring N to its initial state using a reset and then we bring N to the intended state using a transfer sequence and finally we apply w. As a result, resets and transfers are required for each state and transition. Unfortunately, the process of resetting the system (implementing a *reliable reset*) can be expensive or may entail manual configuration. The cost of the resets and transfers is so disruptive that there is a plethora of results aiming to reduce it [28], [35], [36], [61] [65]. A limitation of these methods is that they assume that the W-set is given, and focus on reducing the cost by efficiently combining resets, transfers and the sequences in the W-set. Observe also that there are also methods that do not require there to be a reliable reset, with such techniques returning a single test sequence rather than a set of sequences [33], [35], [36], [44], [59], [60], [66], [67].

The approach presented in this paper requires that the IUT has a reliable reset or a reset sequence. This allows one to construct in polynomial time a test suite that is guaranteed to determine whether the IUT conforms to the specification as long as the IUT has at most some given number of states [5], [7]. Practically, the requirement that there is a reset sequence is not a limiting factor. It is known that the probability of an FSM with n states having a reset sequence is  $1 - \Theta(\frac{1}{n})$  so the higher the number of states of the FSM, the higher the probability of having a reset sequence [68]. In addition, there are systems that can be reset by simply turning the power off and then on again.

Our motivation for the work described in this paper comes primarily from the desire to reduce this cost and enable testers to use W-Sets while deriving test suites from large FSMs. In contrast to previous work, we focus on the problem of choosing a suitable W-set. We introduce a new class of W-Sets that, by design, avoids using (some) resets and transfers. We call such W-Sets Ordered Characterising Sets (O-WSets). The definition of an O-WSet requires that it is possible to execute all of the sequences in W, from all of the states of the FSM M, without using any transfer sequences. However, although an FSM must have a W-set, it may not have an O-WSet. We, therefore, introduce the notion of a Bounded O-WSet (BO-WSet), where transfer sequences are allowed, but there is an upper bound k on their total length.

We first investigate the computation complexity of the problem of deciding whether an FSM has an O-WSet or a BO-WSet. This is phrased as our first research question below: **RQ1** How hard is it to check whether a given FSM possesses an O-WSet or a BO-WSet?

Once we settle this question (in Section IV), we investigate the cost (total number of inputs and number of sequences) of BO-WSets compared to the state-of-the-art (unordered) approach (in Section VI), to answer our next research question: RQ2 Will using BO-WSet reduce the cost of identifying states?

This is further refined into three sub-questions:

**RQ2.1** Will using BO-WSets reduce the total number of inputs (length) required to identify the states?

**RQ2.2** Will using BO-WSets reduce the number of sequences (resets) required to identify the states?

**RQ2.3** Will using BO-WSets reduce the total number of transfer inputs (length) required to identify the states?

After this, we investigate the practical efficiency (time and memory) requirements for deriving BO-WSets, which concerns our third research question:

**RQ3** Is the proposed algorithm for constructing BO-WSets more efficient than the state of the art approaches?

This is refined into the following two sub-questions:

**RQ3.1** How does the time required to construct BO-WSets differ from state-of-the-art approaches for deriving W-Sets? **RQ3.2** How does the memory required to construct BO-WSets differ from state-of-the-art approaches for deriving W-Sets?

Finally, we investigate the implications of using BO-WSets in test suite generation.

**RQ4** Will using BO-WSets lead to more succinct test-suites? This is decomposed into the following two sub-questions:

**RQ4.1** Will using BO-WSets reduce the total number of inputs (length) in test suites?

**RQ4.2** Will using BO-WSets reduce the number of sequences (resets) in test suites?

To answer RQ4 we needed to use a test generation technique. For this task we equipped our testing system with the W-Method [5], [69].

This paper makes the following main contributions.

- We introduce and provide theoretical foundation for O-WSets.

- 2) We show that it is possible to decide in polynomial time whether a given characterising set is an O-WSet. However, the problem of deciding whether a given FSM has an O-WSet is NP-Complete.

- 3) We show that the problem of deciding whether an FSM has a BO-WSet, for a given upper bound *k*, is also NP-Complete.

- 4) We introduce two algorithms, one to derive BO-WSets and one to derive test sequences using BO-WSets. Since the problem of deciding the existence of a BO-WSet is NP-Complete, we do not fix the upper bound *k* but instead aim to produce a BO-WSet that minimises *k*.

- 5) We report the results of experiments that compared the proposed algorithms with the state-of-the-art approaches for *W*-Set generation. These experiments used both industrial and synthetic FSMs.

The second and fourth of these contributions address **RQ1**. The remaining research questions were addressed by the experiments.

This paper is structured as follows. We provide preliminaries in Section II and then explore the motivation for the work in Section III. We formalise the problem and derive its computational complexity in Section IV. We outline the proposed algorithm in Section V and then describe the experimental evaluation in Section VI. We discuss threats to validity in Section VII. Finally, we summarise in Section VIII.

#### II. BACKGROUND

In this section, we provide an overview of the terminology, definitions and concepts used in this paper. We begin with material regarding FSMs and then move to directed graphs.

### A. Finite state machines

**Definition 1** (Finite State Machine). An FSM M is defined by a tuple  $(S, s_1, X, Y, \delta, \lambda)$  where  $S = \{s_1, s_2, ..., s_n\}$  is the finite set of states,  $s_1 \in S$  is the initial state,  $X = \{x_1, x_2, ..., x_p\}$  and  $Y = \{y_1, y_2, ..., y_q\}$  are finite sets of inputs and outputs,  $\delta: S \times X \to S$  is the next state function, and  $\lambda: S \times X \to Y$  is the output function.

Here,  $\times$  denotes the Cartesian-Product between two sets. Given states  $s, s' \in S$ , input  $x \in X$ , and output  $y \in Y$ , when  $\lambda(s,x) = y$  and  $\delta(s,x) = s'$ , we represent this *transition* by a tuple  $\tau = (s,x,y,s')$  and visualise it as  $s \xrightarrow{x/y} s'$ . Transition  $\tau$  has *starting state s, ending state s'*, and *label x/y*. We can interpret

$\tau$  as meaning that if M receives input x when in state s, then it outputs y and moves to s'. Given a set X, we let  $X^*$  denote the set of finite (including empty) sequences of elements of X and let  $X^k$  denote the set of sequences in  $X^*$  of length k. We use  $\varepsilon$  to denote the empty sequence and given sequences  $\bar{x}$  and  $\bar{x}'$ , we write  $\bar{x}\bar{x}'$  to denote the concatenation of  $\bar{x}$  and  $\bar{x}'$ .

We extend the next state and output functions to a sequence of inputs as follows: if  $\bar{x}$  is an input sequence in the form of  $\bar{x} = x\bar{x}'$  then  $\bar{\delta}(s,\varepsilon) = s$ ,  $\bar{\delta}(s,\bar{x}) = \bar{\delta}(\delta(s,x),\bar{x}')$ . Similarly,  $\bar{\lambda}(s,\varepsilon) = \varepsilon$ ,  $\bar{\lambda}(s,\bar{x}) = \bar{\lambda}(\delta(s,x),\bar{x}')$ . By abuse of notation, we abbreviated  $\bar{\delta}$  to  $\delta$  and  $\bar{\lambda}$  to  $\lambda$ .

A path  $\rho$  of M is a sequence  $(s_1,x_1,y_1,s_2)(s_2,x_2,y_2,s_3)\dots$   $(s_k,x_k,y_k,s_{k+1})$  of consecutive transitions and  $\rho$  has starting state  $start(\rho)=s_1$ , ending state  $end(\rho)=s_{k+1}$ , input sequence  $input(\rho)=x_1x_2\dots x_k$ , output sequence  $output(\rho)=y_1y_2\dots y_k$ , and  $label(\rho)=x_1/y_1\dots x_k/y_k$ . The behaviour of an FSM M is defined in terms of the labels of paths leaving the initial state; such labels of paths are called traces.

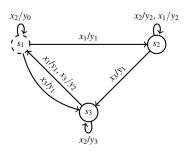

Fig. 1: FSM  $M_1$ . Note that the initial state is highlighted with a dashed line.

An FSM can be graphically represented as a directed graph where the vertices of the graph represent the states of the FSM, and the edges of the graph represent the transitions between the states. Inputoutput labels of the transitions are represented as the labels of the graph's edges. We now define the terms pair set, separating sequence and characterising sets.

**Definition 2** (Pairs Set). Let M be an FSM with the set of states  $S = \{s_1, s_2, ..., s_n\}$ . The pairs set  $\mathcal{S} = \{(s_i, s_j) | i < j \land s_i, s_j \in S\}$  is the set of all pairs we can derive from S. The size of  $\mathcal{S}$  is  $\binom{n}{2} = \frac{n!}{2!(n-2)!} = \frac{n(n-1)}{2}$ .

We can extend  $\delta$  to pair set  $\mathscr{S}' \subseteq \mathscr{S}$  by defining  $\delta(\mathscr{S}', x) = \{(\delta(s, x), \delta(s', x)) | (s, s') \in \mathscr{S}'\}.$

**Definition 3** (Separating Sequence). *Input sequence*  $\bar{x} \in X^*$  separates *states s and s' of FSM M if and only if*  $\lambda(s,\bar{x}) \neq \lambda(s',\bar{x})$ .

**Definition 4** (Characterising Set). *Finite set of input sequence*  $W \subseteq X^*$  *is a* characterising set *for FSM M if for any pair*  $(s,s') \in \mathcal{S}$ , there exists a sequence  $w \in W$  that separates them.

**Example 1.** In Figure 1, we present an FSM  $M_1$  with three states, three inputs, and four outputs. For this FSM, set  $W = \{w_0, w_1\}$ , where  $w_0 = x_1$  and  $w_1 = x_3$ , is a characterising set because the pairs set is  $\mathcal{S} = \{(s_1, s_2), (s_1, s_3)(s_2, s_3)\}$  and  $w_0$  separates pairs  $(s_1, s_2)$  and  $(s_2, s_3)$  and  $w_1$  separates pairs  $(s_2, s_3)$  and  $(s_1, s_3)$ .

Transitions with the same input and output might start from different states and end in the same state. For such transitions, the input is a *merging* input, as defined below.

**Definition 5** (Merging Inputs). Given  $(s,s') \in \mathcal{S}$ , input  $x \in X$  is a merging input for (s,s'), when  $\delta(s,x) = \delta(s',x)$  and  $\lambda(s,x) = \lambda(s',x)$ ,

An FSM is *minimal* if all states are pairwise *separable*. There are several practical benefits of using characterising sets. First, every (minimal) FSM has a characterising set. In addition, if a minimal FSM M has n states, then for every pair s,s' of distinct states of M, there must be an input sequence of length at most n-1 that separates s and s'. We observe that any FSM can be converted into an equivalent minimal FSM [70] and so we only consider minimal FSMs.

For efficiency reasons, using a non-redundant characterising set, defined below, is desirable. Intuitively, a characterising set is non-redundant when one cannot form a smaller characterising set by removing or replacing a sequence with a proper prefix.

**Definition 6** (Redundant Characterising Set). A characterising set W is redundant if one of the following conditions holds:

- 1) there is some  $w \in W$  such that  $W \setminus \{w\}$  is a characterising set; or

- 2) there is some  $w \in W$  with a proper prefix w' such that  $W \cup \{w'\} \setminus \{w\}$  is a characterising set.

If a characterising set W is not redundant, then it is said to be non-redundant.

As noted above, it is always possible to construct a characterising set whose sequences all have length at most n-1. Importantly, if a characterising set is non-redundant, then it has at most n-1 input sequences.

**Proposition 1.** If M is an FSM with n states and W is a non-redundant characterising set for M then  $|W| \le n-1$ .

*Proof.* We use proof by contradiction, assuming that there is an FSM M with n states that has a non-redundant characterising set W such that |W| > n - 1.

We can order the sequences in W to form  $w_1, \ldots, w_k$  and for all  $0 \le j \le k$  let  $W_j = \{w_1, \ldots, w_j\}$  (so  $W_0$  is the empty set). Then a set  $W_j$  defines an equivalence relation  $\sim_j$  on the set S of states of M defined by:  $s \sim_j s'$  if and only if  $\lambda^*(s, w_\ell) = \lambda^*(s', w_\ell)$  for all  $1 \le \ell \le j$ . A set of states that are equal under a relation  $\sim_j$  forms an equivalence classes of the states.

Clearly, all states of M are equivalent under the relation  $\sim_0$ , and no pair of states of M is equivalent under  $\sim_k$  (since  $W_k = W$  is a characterising set for M). Thus,  $\sim_0$  has 1 equivalence class and  $\sim_k$  has n equivalence classes. Since  $k \geq n$ , we must have that there exists  $0 \leq \ell < k$  such that  $\sim_\ell$  and  $\sim_{\ell+1}$  have the same number of equivalence classes and so  $\sim_\ell = \sim_{\ell+1}$ . But this implies that  $\{w_1, \ldots, w_\ell\}$  and  $\{w_1, \ldots, w_{\ell+1}\}$  separate the same pairs of states. We can, therefore, deduce that if  $w_{\ell+1}$  separates states s and s' of M, then there exists some other input sequence in W that separates s and s'. As a result,  $W \setminus \{w_\ell\}$  is a characterising set for M. This contradicts W being non-redundant as required.

As a result, for an FSM M with n states, we consider characterising sets that are non-redundant and that contain at most n-1 input sequences of length at most n-1.

In order to test a transition that has starting state s, the FSM M must be brought to state s. To achieve this, normally M is reset by applying a reliable reset operation (r) and brought to the designated state using a reaching sequence. We now define the reaching sequence set.

**Definition 7** (Reaching Sequence Set). A prefix-closed set of input sequences  $\mathscr{RS}$  is a reaching sequences set (RSS) for FSM M with initial state  $s_1$ , if and only if for all  $s \in S$ , there exists an input sequence  $\bar{x}$  in  $\mathscr{RS}$  such that  $\delta(s_1, \bar{x}) = s$ .

Note that a sequence in RSS is used to transfer the FSM from the initial state to another; therefore, RSSs are also transfer sequences also covers RSSs. Finally, we can formally define state identification sequences (set) as follows.

**Definition 8** (State Identification Set). Let W be a non-redundant characterising set and  $\mathscr{RS}$  a RSS for FSM M. Then, the set of input sequences  $\mathscr{T} = \{r\bar{x}w | \bar{x} \in \mathscr{RS} \land w \in W\}$  is a state identification set (SIS) for FSM M.

In addition to state identification, SISs can be used to derive test suites. A test suite for FSM M is a set of input sequences that separates M from every faulty implementation N in a given fault domain. The classical fault domain is characterised by transfer faults (transitions ending in the wrong state), state faults (states that are not implemented correctly), output faults (outputs are not implemented correctly), and hybrid faults (a mixture of two or more faults given above).

The most widely used W-set based test suite generation method is the W-Method [5], [69]. In this approach, in addition to SIS, a *Transition Verification Set (TVS)* is also built.

**Definition 9** (Transition Verification Set). Let W be a non-redundant characterising set and  $\mathscr{RS}$  an RSS for FSM M. Then, the set of input sequences  $\mathscr{T}s = \{r\bar{x}xw|\bar{x} \in \mathscr{RS} \land x \in X \land w \in W\}$ , where X is the finite set of inputs of M, is a transition verification set (TVS) for FSM M.

Once a TVS has been built, the W-Method unites SIS and TVS by removing sequences that are prefixes of other sequences. Let PR() denote the prefix elimination operation. A test suite with respect to the fault domain given above can be defined as follows.

**Definition 10** (Test Suite (TS)). The set  $TS = PR(SIS \cup TVS)$  of input sequences is a Test Suite (TS) for M.

## B. Directed graphs

A directed graph is defined by tuple G = (V, E) where V is a finite set of vertices,= and E is a finite set of directed edges between vertices. An edge is defined by a tuple $(v_i, v_j, l)$ , where  $v_i$  is the source vertex,  $v_j$  is the destination vertex, and l is the label. For a given vertex  $v_i$ , the number of edges with  $v_i$  as the destination vertex is that vertex's in-degree. Similarly, the number of edges having  $v_i$  as the source vertex is the out-degree of that vertex. Starting from a vertex  $v \in V$ , one can reach another vertex  $v' \in V$  by traversing edges of this graph, without repeating an edge, forming a graph-path. A directed graph is strongly-connected if for every pair of vertices  $v_i$ ,  $v_j$ , there exists a graph-path that starts at  $v_i$  and reaches  $v_j$ . For

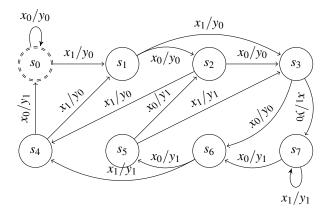

Fig. 2: Example FSM  $M_1$  ShiftRegister from [72].

a given initial vertex, if a graph-path visits every edge of the graph exactly once, it is an *Euler path*. Not all directed graphs have an Euler path. A directed graph has an Euler path if and only if it satisfies the following conditions [71].

- 1) The graph is strongly connected,

- 2) There exists a vertex with (out-degree)-(in-degree)=1,

- 3) There exists a vertex with (in-degree)-(out-degree)=1,

- 4) For every other vertex, the in-degree and out-degree values are the same.

#### III. MOTIVATION

Every minimal FSM has a W-set, making them popular in FSM-based testing. For example, some automata learning algorithms construct W-sets to derive test sequences (test suites) [45]. One fundamental drawback of using W-sets is that for every sequence in the test suite, the tester has to carry out a *reset operation*, which is costly. This cost may stem from the manual configuration of the test environment or using expensive features to bring the underlying system back to its initial state. This cost increases when the underlying system has many states. Recent studies aim to generate compact characterising sets to reduce this cost [40].

Inspired by this observation, we devise an algorithm to derive a type of W-set with the aim of minimising the number of resets used in testing. To better position our work, we consider two well-known W-set generation algorithms, namely, the Classical W-set generation algorithm (CWA) [5], and the state-of-the-art Minimum Characterising Set Algorithm (MWA) [40]. In the rest of this section, we briefly review the two algorithms, apply them to a small example and identify their shortcoming, hence motivating the contributions of the approach to the state of the art.

The CWA operates on the notion of k-separability. If an input separates a pair of states, these states are 1-separable. If there is an input sequence of length 2 that separates a pair of states, then they are 2-separable. If a pair is separable by an input sequence of length k, they are k-separable. The construction of the characterising set uses this notion and builds separating sequences of length k by using the separating sequences of length k-1. Note this computation scheme will lead to redundant characterising sets (Definition 6). Once all the pairs, i.e., elements of the pairs set, are separated, the

prefixes of other sequences are removed, and the remaining set is returned. We picked the CWA method because it is the most efficient algorithm that does not rely on heuristics and many of the industrial systems for machine inference such as LearnLib [55], [56], and AalPy [58] use this method.

As the proposed approach aims to reduce the transfer sequences, we need a benchmark *W*-set generation method with a similar flavour. Recently, Türker et al. introduced the MWA to derive a smallest *W*-set in terms of the number of input sequences that it contains [40]. Their motivation is to reduce the cost of transfer sequences (and so the cost of testing) by reducing the number of sequences of *W*-sets. The authors showed that such an endeavour is PSPACE-Complete [40]. The MWA algorithm is a greedy method that uses a breadth-first search to construct *W*-sets by selecting promising separating sequences based on their separability facilities [40]. Since, to our knowledge, the MWA is the most recent and the most efficient method aiming to reduce the cost of testing by constructing compact *W*-sets we picked this approach as another baseline algorithm for this work.

**Example 2.** In Figure 2, we are given an FSM ShiftRegister modelling a real-circuit [72]. For the FSM ShiftRegister, the CWA can generate a W set  $W = \{x_0x_0, x_0x_1x_0, x_1x_1x_1\}$ . After removing the prefixes, the state identification set (of sequences) is given as follows  $\alpha_1 = \{rx_0x_0, rx_0x_1x_0, rx_1x_0x_0x_1x_0, rx_1x_0x_1x_1, rx_1x_1x_0x_1x_0, rx_1x_0x_1x_0, rx_1x_0x_1x_0, rx_1x_0x_1x_1, rx_1x_1x_0x_0x_0, rx_1x_0x_1x_0, rx_1x_0x_1x_1, rx_1x_1x_0x_0x_0, rx_1x_1x_0x_0x_0, rx_1x_1x_1, rx_1x_1x_0x_0x_1, rx_1x_1x_0x_0, rx_1x_1x_1, rx_1x_1x_0x_0, rx_1x_1x_1, rx_1x_1x_0x_0, rx_1x_1x_1, rx_1x_1x_1x_0, rx_1x_1x_1x_1, rx_1x_1x_1x_1x_1, rx_1$

The set  $\alpha_1$  has 19 sequences requiring 19 reset operations with 99 inputs. Moreover, 47 inputs (in red) out of 99 are transfer sequences. 52% of the sequences are used for testing (input utilisation).

Applying MWA to this FSM generates the singleton set  $W = \{x_0x_1x_0x_1\}$ . In this case the state identification set  $\alpha_2$  would be  $\alpha_2 = \{rx_0x_1x_0x_1, rx_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1, rx_1x_1x_0x_0x_1x_0x_1\}$ .  $\alpha_2$  has 7 sequences, requiring seven reset operations. The total number of inputs is 45, of which 17 are for transfer<sup>1</sup>, bringing input utilisation up to 62.2%.

In this work, we increase input utilisation by reducing the use of transfer sequences; note that input utilisation is inversely proportional to the size of transfer sequences.

The sequence  $\alpha_3$ , automatically generated by the algorithm proposed in this paper, contains a single input sequence and requires only one reset operation. Moreover, it has 57 inputs, ten of which are for transfer, which increases input utilisation to 82%.

<sup>&</sup>lt;sup>1</sup>28 out of 45 inputs are used for testing, therefore 100 \* 28/45 = 62.2.

This example shows that an appropriate choice of *W*-set can reduce the use of resets and transfer sequences in testing.

#### IV. ORDERED CHARACTERISING SETS

In this section, we explore the problem of finding a 'good' characterising set for an FSM M.<sup>2</sup> Test generation techniques typically use a characterising set to check a state s by separating s from other possible states. As part of this, many test techniques have a verification phase that checks the application of sequences from W to states of the IUT.

We would like to efficiently verify the characterising set W. This verification step involves checking the result of applying every member of W to every state of M and so we start by defining terminology for a single  $w \in W$  and state  $s \in S$ .

**Definition 11** (State-Identifying Path). A state-identifying path (SIP)  $\alpha$  for state s is a path starting from s with  $input(\alpha) \in W$ .

We would like to execute every element of W from every state in S, which defines  $|S| \times |W|$  state-identifying paths. We would like to use a single test sequence (defined by a path through the FSM) that includes all of these state-identifying paths. In the following,  $\beta_i$  denotes a transfer sequence that brings the underlying FSM from one state to another state.

**Definition 12** (Identification Path). Given FSM M and characterising set W for M, a path  $\bar{p}$  is an identification path for W if  $\bar{p}$  can be written in the form  $\alpha_1 \beta_1 \alpha_2 \beta_2 \dots \alpha_k$  such that the following constraints hold:

- 1)  $start(\bar{\rho}) = s_1$

- 2) For all  $1 \le i \le k$ , we have that input  $(\alpha_i) \in W$ .

- 3) For all  $\alpha_i, \alpha_j, 1 \le i < j \le k$ , it holds that  $input(\alpha_i) \ne input(\alpha_i)$  or  $start(\alpha_i) \ne start(\alpha_i)$ .

- 4) For all  $s \in S$  and  $w \in W$  there exists  $1 \le i \le k$  such that  $input(\alpha_i) = w$  and  $start(\alpha_i) = s$ .

Here, the  $\alpha_i$  are identification paths, and the  $\beta_i$  are transfer sequences that connect these identification paths. Ideally, we would like the identification path for W to include no additional transfer sequences (and so be optimal). This is captured by removing the  $\beta_i$  above. In this work, we focus on deriving identification paths that have no  $\beta_i$ 's. This type of identification path is formally defined below.

**Definition 13** (Transfer Free State Identification Path). Given FSM M, a Transfer Free State Identification Path  $\bar{\rho}$  for characterising set W is a path of M that can be written in the form  $\alpha_1 \alpha_2 ... \alpha_k$  such that the following constraints hold:

- 1)  $start(\bar{\rho}) = s_1$

- 2) For all  $1 \le i \le k$ , we have that input  $(\alpha_i) \in W$ .

- 3) For all  $\alpha_i, \alpha_j, 1 \le i < j \le k$ , it holds that  $input(\alpha_i) \ne input(\alpha_i)$  or  $start(\alpha_i) \ne start(\alpha_j)$ .

- 4) For all  $s \in S$  and  $w \in W$  there exists  $1 \le i \le k$  such that  $input(\alpha_i) = w$  and  $start(\alpha_i) = s$ .

The above property is desirable since it tells us that we can verify W without the use of additional transfer sequences.

However, this property does not preclude the possibility that the chosen characterising set W is a relatively expensive way of separating states of M and so of checking transitions of the IUT in testing: The (prefixes of) sequences in W used to separate states may be longer than necessary. The following defines what it means for a characterising set W to be minimal: It should allow the shortest possible input sequences to be used to separate states.

**Definition 14** (Minimal Characterising Set). Given FSM M, a characterising set W for M is said to be minimal if for all  $s,s' \in S$  with  $s \neq s'$  there is a prefix w' of a sequence w in W such that the following conditions hold.

- 1) w' separates s and s'; and

- 2) no shorter input sequence separates s and s'.

The definition of a characterising set does not ensure that either of the above conditions hold. For example, if W is a characterising set and  $\bar{x}$  is a sequence that is not in W then  $W \cup \{\bar{x}\}$  is also a characterising set. Naturally, one might expect any algorithm that generates a characterising set to aim to produce one that is minimal.

Importantly, it is possible to check whether a characterising set W is minimal in polynomial time. The proof of the following result is based on showing that one can determine the length of the shortest input sequence that separates two states s and s' of an FSM M in polynomial time.

**Proposition 2.** It is possible to decide whether a characterising set W for FSM M is minimal in polynomial time.

We seek optimal W sets that have both of these properties, i.e., they are minimal and also they can be verified without the use of additional transfer sequences. We capture both with the following conditions.

**Definition 15** (Ordered characterising Set). Let M be an FSM with n states. A non-redundant characterising set  $W_o = \{w_1, w_2, \dots, w_m\}$  is an Ordered characterising Set (O-WSet) for M if the following properties hold:

- 1)  $W_o$  is minimal; and

- 2) there exists a Transfer Free State Identification Path  $\bar{\rho}$  for  $W_o$ .

As one might expect, we do not need to consider input sequences of length greater than n-1, when considering alternative W set for an FSM with n states.

**Proposition 3.** If FSM M has n states and W is a non-redundant and minimal characterising set for M, then no sequence in W has a length greater than n-1.

We have the problem of checking whether a given characterising set is an O-WSet.

**Definition 16** (Ordered Characterising Set Checking problem). Given a characterising set W for FSM M, the O-WSet checking problem is to decide whether W defines an O-WSet for M.

The proof of the following result follows from it being possible to decide in polynomial time whether W is minimal (Proposition 2) and it being possible to express whether W

<sup>&</sup>lt;sup>2</sup>Proofs of the results can be found in the supplementary material.

has a corresponding Transfer Free State Identification Path in terms of whether a particular graph has an Euler Path.

**Proposition 4.** The O-WSet checking problem is polynomial time solvable.

If we simply generate a characterising set W for an FSM M, then W may not be an O-WSet for M. The following shows that an FSM may not have an O-WSet.

**Example 3.** Given n > 1 define an FSM  $M^n$  that has two inputs  $x_1$  and  $x_2$  and n outputs  $o_1, \ldots, o_m$ . The transitions are defined by the following.

- 1) The input of  $x_1$  simply cycles the state with constant output  $o_1$ . Thus, for all  $1 \le i \le n$ , we define  $\lambda(s_i, x_1) = o_1$  and  $\delta(s_i, x_1) = s_i$  where  $j = i + 1 \mod n$ .

- 2) The input of  $x_2$  maps all states to the initial state and provides a unique output. Specifically, for all  $1 \le i \le n$ , we define  $\lambda(s_i, x_2) = o_i$  and  $\delta(s_i, x_2) = s_1$ .

Observe that an input sequence separates two or more states if and only if the input sequence contains input  $x_2$ . Further, such an input sequence separates all pairs of states, i.e., all elements in set  $\mathscr{S}$ . We can, therefore, conclude that any non-redundant characterising set W contains exactly one input sequence w and w must include input  $x_2$ . One can now observe that, since w contains input  $x_2$ , the input of w maps all states to the same state of M: for all  $1 \le i < j \le n$  we have that  $\bar{\delta}(s_i, w) = \bar{\delta}(s_j, w)$ . It is straightforward to see that such a characterising set cannot be an O-WSet since n > 1.

We are therefore interested in the problem of deciding whether an FSM M has an O-WSet.

**Definition 17** (Ordered Characterising Set problem (O-WSet problem)). Given an FSM M, the O-WSet problem is to decide whether M has an O-WSet  $W_o$ .

We now explore the computational complexity of this problem. First, we can place a polynomial upper bound on the size of any O-WSet since if an FSM M has n states, then every non-redundant characterising set of M has at most n-1 sequences (Proposition 1), each of which has at most n-1 inputs (Proposition 3). Thus, a non-deterministic Turing Machine can decide whether M has an O-WSet by guessing a possible O-WSet M and checking in polynomial time whether M is an O-WSet for M (Proposition 4). We therefore have the following.

# **Proposition 5.** The O-WSet problem is in NP.

The O-WSet problem is actually NP-Complete. The proof that the problem is NP-Hard involves mapping an instance of the 3-Exact Cover problem to an instance of the O-WSet problem. The 3-Exact Cover problem is known to be NP-Complete [73].

#### **Theorem 1.** The O-WSet problem is NP-complete.

We have seen that an FSM need not have an O-WSet (Example 3). In practice, we might instead wish to place a bound on the size of the transfer sequences used.

**Definition 18** (Bounded Ordered characterising Set). Let M be an FSM with n states and  $k \ge 0$  be an integer. A non-redundant characterising set  $W_o = \{w_1, w_2, \dots, w_m\}$  is a Bounded Ordered characterising Set (BO-WSet) for M and k if the following properties hold:

- 1)  $W_o$  is minimal; and

- 2) there exists a State Identification Path  $\bar{\rho}$  for  $W_o$  such that the sum of the lengths of the transfer sequences is at most k.

Note that for the FSM given in Figure 1, the W-set  $W = \{x_1x_2\}$  is a BO-WSet where k = 1 and the input sequence  $\bar{x} = x_1x_2, x_1x_2, x_3, x_1x_2$  from  $s_1$  is a state identification path and the length of the transfer sequence is k = 1  $(x_3)$ .

**Definition 19** (Bounded O-WSet problem). Given an FSM M and integer  $k \ge 0$ , the Bounded O-WSet problem is to decide whether M has a Bounded O-WSet  $W_0$  for M and k.

The existence problem for a given k and FSM M is NP-Complete. In the following, the problem being NP-hard is immediate since we can set k = 0 and refer to Theorem 1.

**Theorem 2.** The bounded O-WSet problem is NP-complete.

This also implies that the problem of finding a state identification path with a minimal total length of transfer sequences cannot be solved in polynomial time (unless P=NP) and so it addresses **RQ1**. Motivated by this, we now develop an algorithm to find a Bounded O-WSet for a small bound. The algorithm developed is a heuristic (it is not guaranteed to return an optimal solution), and we report on experiments that evaluated this algorithm in Section VI.

### V. ALGORITHM FOR DERIVING BO-WSETS

## A. High-level summary

Our algorithm computes a state identification path in two steps: first, using a heuristic, it builds a bounded ordered characteristic set  $(W_o)$ . Then, it uses  $W_o$  to build a state identification path. In the remainder of this section, we describe these two procedures.

#### B. Computing a BO-WSet

The BO-WSet generation algorithm is presented in Algorithm 1. In summary, the algorithm constructs a BO-WSet  $W_o$  in a sequence-by-sequence fashion where each sequence is built input-by-input. To achieve this, the algorithm first creates an empty BO-WSet  $(W_o)$  and a set of all unseparated pairs of states  $(\mathcal{S}^l)$ , which is initialised as the pairs set  $(\mathcal{S}^l)$ ; see Definition 2 and Lines 1-2 of Algorithm 1). After this, it enters a loop (the Outer-Loop) (Lines 3-15 of Algorithm 1). The Outer-Loop terminates when all pairs are separated. As noted in Definition 2, there are n(n-1)/2 such pairs; therefore, the number of iterations of the Outer-Loop is of  $O(n^2)$ .

At each iteration of the Outer-Loop, the algorithm first initiates two empty input sequences  $(\bar{x}, \bar{x}^*)$  and enters another loop (the Inner-Loop) (Lines 5-14 of Algorithm 1). The Inner-Loop aims to generate a separating sequence that separates at least one pair from  $\mathcal{S}'$ . Proposition 3 tells us that the

**Algorithm 1:** Bounded ordered characterising set generation algorithm.

```

input : M = (S, X, Y, \delta, \lambda)

output: An ordered characterising set as W_0

W<sub>o</sub> ← ∅

2 \mathscr{S}' \leftarrow \mathscr{S}, V \leftarrow \emptyset.

3 while \mathcal{S}' is not empty do

// Outer-Loop.

\bar{x} = \varepsilon, \bar{x}^* = \varepsilon

while |\bar{x}| \le n-1 and \mathcal{S}' has items do

// Inner-Loop.

\xi \leftarrow set of inputs that can separate some pairs from \mathscr{S}'.

// If no separating input exists, then \xi=X .

\xi' \leftarrow argmax |\delta^o(\mathcal{S}', x)|

7

/* Select based on order-friendliness.

\xi'' = argmax \ occ(\bar{x}, x)

// Select based on overlap-friendliness.

x = Rand(\xi'')

// Break-ties.

10

if \bar{x} separates unmarked pairs from set \mathscr{S}' then

12

\bar{x}^{\star} = \bar{x}

Move separated pairs from \mathcal{S}' to V.

13

\mathscr{S}' \leftarrow \delta(\mathscr{S}', x)

14

if \bar{x}^* is not empty then

15

W_o \leftarrow W_o \cup \{\bar{x}^{\star}\}

16

\mathcal{S}' \leftarrow \mathcal{S}, and using V, marks separated elements of \mathcal{S}'.

17

18 return Wo

```

maximum length of such a sequence is n-1, and therefore it iterates at most n-1 times.

At each iteration of the Inner-Loop, the algorithm tries to find a *good* input x to be concatenated to  $\bar{x}$  based on *separability* and two independent heuristics: *order-friendliness*, and *overlap-friendliness*, explained below.

**Separability:** During the Inner-Loop, the algorithm first tries to return a set  $(\xi)$  of inputs that separate at least one pair from set  $\mathcal{S}'$ ; however, if no input separates any of the pairs from set  $\mathcal{S}'$ , then we set  $\xi$  as the set X, i.e.,  $\xi = X$ . Orderfriendliness: Order-friendliness is a heuristic method that makes it more likely that a member of  $W_o$  brings the FSM to a state from which a member from  $W_0$  can be applied without the need of a transfer sequence. With this heuristic, application of sequences from  $W_0$  will less likely require a transfer sequence After forming  $\xi$ , the algorithm searches for a subset  $(\xi')$  of  $\xi$ according to order-friendliness value ( $|\delta^0|$ ), which is defined as the number of different states the FSM will reach from  $\mathscr{S}'$  (Lines 6-7 of Algorithm 1). The set  $\delta^0(\mathscr{S},x)$  is formally defined as  $\delta^0(\mathscr{S},x) = \{\delta(s,x) | \exists s'.(s,s') \in \mathscr{S} \lor (s',s) \in \mathscr{S} \}.$ The higher the value of  $|\delta^0|$ , the better the order-friendliness is.

**Overlap-friendliness:** Once the set  $\xi'$  is constructed, the algorithm constructs a subset  $(\xi'')$  of  $\xi'$  according to the *overlap friendliness value*, which is defined as the number of occurrences of input symbol x in the current sequence  $\bar{x}$  (Line 8 of Algorithm 1). We use the  $occ(\bar{x},x)$  function to retrieve the overlap friendliness value, which is the number of occurrences of input x in  $\bar{x}$ . Overlap-friendliness aims to create sequences

retaining similar input symbols to promote overlapping. If two inputs have the same value for this, the algorithm selects one randomly (Line 9 of Algorithm 1).

After this, the algorithm appends the input to  $\bar{x}$  and then checks whether the new input sequence separates a pair. If not, the algorithm proceeds; otherwise, the algorithm assigns this input sequence to  $\bar{x}^*$  (Lines 10-13 of Algorithm 1). Copying  $\bar{x}$  to  $\bar{x}^*$  prevents i) the addition of input sequences that do not separate a pair and ii) the addition of input sequences that have redundant post-fixes. After the input is appended, the algorithm adds the indices of newly separated pairs to V (Line 13 of Algorithm 1). Afterwards, the next states reached from  $\mathscr{S}'$  are calculated (Line 14 of Algorithm 1).

Once the Inner loop terminates, the algorithm updates the  $W_o$  set if  $\bar{x}^*$  is not an empty sequence and then resets  $\mathscr{S}'$  (Lines 15-17 of Algorithm 1). Finally, once the BO-WSet is constructed, the algorithm returns this set (Line 18 of Algorithm 1). Since the upper-bound on the number of pairs in  $\mathscr{S}$  is  $O(n^2)$  and the Inner-loop iterates at most O(n) times, Algorithm 1 requires  $O(n^3)$  steps of computation.

Running example: Consider the FSM given in Figure 2. Initially the set  $\mathcal{S}'$  (and  $\mathcal{S}$ ) has all the pairs i.e.  $\mathcal{S}' = \{(s_0, s_1), (s_0, s_2), \dots, (s_6, s_7)\}$ . After the execution of line 6 of Algorithm 1, we have the set  $\xi = \{x_0, x_1\}$  as both inputs pairwise separate some elements from set  $\mathscr{S}'$ . However, among these inputs, the highest order-friendliness value belongs to the input  $x_0$  as  $\delta^0(\mathcal{S}', x_0) = \{s_0, s_2, s_3, s_5, s_6\}$ . For  $x_1$ , we would have  $\delta^0(\mathscr{S}', x_1) = \{s_1, s_3, s_4, s_7\}$ . Since  $\xi'$ has one element the algorithm forms the set  $\xi'' = \{x_0\}$  and proceeds to line 14 of Algorithm 1 after moving the separated pairs to V ( $V = \{(s_0, s_4), (s_0, s_5), (s_0, s_6), (s_0, s_7), (s_1, s_4), \}$  $(s_1, s_5), (s_1, s_6), (s_1, s_7), (s_2, s_4), (s_2, s_5), (s_2, s_6), (s_2, s_7),$  $(s_3, s_4), (s_3, s_5), (s_3, s_6), (s_3, s_7)\}$ ) and appending  $x_0$  to  $\bar{x}^*$ . Then, at line 14, the set  $\mathcal{S}'$  is updated by applying  $x_0$  to the remaining members of  $\mathcal{S}'$ , leading to  $\mathcal{S}' = \{(s_0, s_2), (s_0, s_3),$  $(s_0, s_6), (s_2, s_3), (s_2, s_4), (s_0, s_5), (s_2, s_5), (s_2, s_6), (s_5, s_6)$ .

In the second round of the loop,  $\xi'$  returns  $\{x_0, x_1\}$  as both inputs separate some pairs and lead to  $|\delta^0(\mathscr{S}', x_0)| = |\delta^0(\mathscr{S}', x_1)|$  (both have five elements). At this point, as line 8 of Algorithm 1 dictates, the algorithm selects input  $x_0$  as  $\bar{x}^* = x_0$ . After executing line 13, we have  $\mathscr{S}' = \{(s_0, s_2), (s_2, s_3), (s_5, s_6)\}$  and after line 14 we have  $\mathscr{S}' = \{(s_0, s_3), (s_3, s_6), (s_2, s_5)\}$  and  $\bar{x}^* = x_0 x_0$ .

In the third iteration, as both inputs  $x_0$  and  $x_1$  can pairwise separate states from set  $\mathscr{S}'$  we have  $\xi = \{x_0, x_1\}$ . However  $\xi' = \{x_0\}$  as the cardinality of the set  $|\delta^0(\mathscr{S}', x_0)| > |\delta^0(\mathscr{S}', x_1)|$ . Which (after line 13) leads to set  $\mathscr{S} = \{(s_0, s_3)\}$ . After line 14, we have  $\delta(\mathscr{S}', x_0) = \{(s_0, s_6)\}$ . Clearly, after this iteration the algorithm sets  $\xi' = \{x_0, x_1\}$  but due to the overlap-friendlines sets  $\xi'' = \{x_0\}$ , which leads to the termination of the algorithm with  $\bar{x}^* = x_0 x_0 x_0 x_0$ .

# C. Computing a state identification path

The steps in constructing a state identification path are given in Algorithm 2. The algorithm (BOWA) begins by receiving a

<sup>&</sup>lt;sup>3</sup>Please note that we do not explicitly write the contents of set V.

BO-WSet and building a directed graph  $G_o = (V, E \cup E')$  using this BO-WSet (Lines 1-2 of Algorithm 2).

The graph  $G_o$  has two classes of edges and is constructed as follows. For each state s of the FSM, the algorithm introduces a vertex v(s) to  $G_o$ , and for each transition  $\tau = (s,x,y,s')$ , it introduces an edge e = (v(s),v(s')) with label x/y to E. Furthermore, for each sequence  $\bar{x} \in W_o$  and for each state  $s \in S$ , it introduces an edge from v(s) to  $v(\delta(s,\bar{x}))$  with label  $\bar{x}/\lambda(s,\bar{x})$  in E'. This graph has n vertices and  $(n*|X|) + |W_o|$  edges.

After this, the algorithm checks whether  $G_o$  satisfies the Euler Path conditions on edges E' given in Section II-B. If so, this path corresponds to the state identification path, and the algorithm returns the label of such a path as the state identification path (Lines 3-4 of Algorithm 2).

Otherwise, the algorithm constructs a state identification path through a heuristic that minimises the use of transfer sequences. The heuristic step deployed in this algorithm

**Algorithm 2:** BO-Wsets-based state identification path generation algorithm (BOWA).

```

input : M = (S, X, Y, \delta, \lambda), W_o

output: State identifying path

1 W_o \leftarrow BO\text{-}Wset(M)

2 Construct G_o = (V, E \cup E') using M and W_o, \rho' \leftarrow \emptyset.

3 if Euler path exists then

Return the label of the path \rho' and terminate.

5 Compute all-pair shortest paths using edges E on G_o.

6 foreach v \in V do

Compute (cost(v)) the total length of shortest paths

leaving v using G_o and set the number of outgoing E'

edges of v as unv(v).

8 v^* \leftarrow V(s_0)

9 while not all sequences in W_0 are applied at every state in

set S do

\chi \leftarrow argmax \ cost(v)

10

v \in adj(v^*)

// Select vertex with largest cost.

\chi' \leftarrow argmax \ unv(v)

// Select vertex with largest unvisited edges.

if \chi' \neq \emptyset then

12

v^* \leftarrow Rand(\chi'), unv(v) \leftarrow unv(v) - 1

13

// Break-ties.

Add edge e = (v^*, v) to path \rho', v^* \leftarrow v

14

15

Find a path \rho from v^* to a vertex having maximum

16

cost(v) and unv(v) values.

\rho' \leftarrow \rho' \rho, v^* \leftarrow v

18 Return \rho'

```

prioritises edges emanating from vertices having a higher cost for visiting other vertices, i.e. selects vertices with the highest  $\Sigma_{v' \in V} SP(v,v')$  where SP is the length of the shortest path from v to v'. Doing this reduces the chance of reaching a vertex and selecting an edge that requires longer transfer sequences. To achieve this, the algorithm computes the all-pair shortest paths between the vertices of  $G_o$  using the edges in E and

| Names                                | States | inputs |

|--------------------------------------|--------|--------|

| dk14                                 | 7      | 8      |

| mc                                   | 4      | 8      |

| dk15                                 | 4      | 8      |

| dk16                                 | 27     | 4      |

| dk17                                 | 8      | 4      |

| dk27                                 | 7      | 2      |

| keyb                                 | 19     | 24     |

| lion9_with_loops                     | 9      | 4      |

| lion_with_loops                      | 4      | 4      |

| lion_with_loops_with_hidden_states   | 4      | 4      |

| opus_with_sink                       | 10     | 11     |

| s27_with_loops                       | 5      | 12     |

| shiftreg                             | 8      | 2      |

| tma_with_loops                       | 20     | 6      |

| train11_with_loops                   | 9      | 4      |

| train4_with_loops                    | 4      | 4      |

| train4_with_loops_with_hidden_states | 5      | 4      |

| train4_with_sink                     | 5      | 4      |

TABLE I: The benchmark FSMs used.

then for each vertex  $v \in V$  of  $G_o$ , it computes the sum of the total shortest paths  $(cost(v) = \Sigma_{v' \in V}SP(v,v'))$ , denoted by cost(v). While doing this, the algorithm also stores the number of outgoing E' edges from v represented as unv(v). The value of unv(v) is used to keep the number of unvisited E' edges emanating from vertex v and, therefore, is updated at every visit (Lines 5-7 and 13 of Algorithm 2).

Then, the algorithm selects the vertex corresponding to the initial state of M ( $v(s_0)$ ) as the *current vertex* and enters a loop. At each iteration of the loop, the algorithm first finds a set of vertices ( $\chi$ ) having maximum cost and then finds a subset ( $\chi'$ ) of these vertices having maximum unvisited edges, randomly picks one edge of a vertex from  $\chi'$ , and adds this to  $\rho'$  (Lines 10-14 of Algorithm 2).

However, if no such  $\chi'$  exists, then the algorithm retrieves the shortest path  $\rho$  from the current vertex  $v^*$  to a vertex having maximum cost(v) and unv(v) values and appends it to the end of  $\rho'$  (Lines 15-17 of Algorithm 2). Finally, the algorithm terminates after returning the path it constructs (Line 18 of Algorithm 2). Since the underlying FSM is connected, the algorithm is guaranteed to return a state identification path.

Due to construction of graph G, Euler path, and all-pairs shortest paths, we need  $O(n^3) + O(n^3) + O(n^3) = O(n^3)$  steps of computation. Computing cost(v) and unv(v) require  $O(n^2)$  steps of computation. The *While* loop iterates  $O(n^2)$  times where at each iteration it has to find a path using a BFS search in the worst case which needs O(n+p) steps of computation where p is the number of inputs. So Algorithm 2 needs  $O(n^3)$  steps of computation assuming p is less than p. This cubic time requirement is a limiting factor for processing large FSMs.

## VI. EXPERIMENTS

In this section, we provide the results of controlled experiments and use them to answer our research questions two, three, and four.

We first provide information regarding the software and experimental setup; then, we introduce our test subjects. Afterwards, we describe the structure of the experiments and the visual encodings used in presenting the results. Finally, we present the experiment results.

### A. Experiment setup

11th Gen Intel(R) Core(TM) used an 11800*H* @ 2.30GHz CPU having 24MB cache, paired 32GB DDR4 memory on Intel(R)WM590 chipset. We implemented the algorithms in C++ using Microsoft Visual Studio 19. We used the R tool to generate plots and conduct statistical analysis [74]. For reproducibility reasons, we provide the C++ code, data (FSM specs, constructed sequences) and the R tool scripts for producing the results and illustrations, https://github.com/urazc/OrderedWSets. During experiment, we used the GetProcessMemoryInfo function with PeakWorkingSetSize to compute the number of memory pages kept in RAM by the operating system. When comparing the memory requirements, we ignored the memory used for storing the FSMs and just compared the memory needed for the data structures used by the algorithms. Moreover, in order to measure the time required for an algorithm to build W-sets, we used the high resolution clock::now() interface of the chrono.h library. Throughout the experiments, we did not allow algorithms to run for more than 120 seconds in order to complete the experiments in a reasonable amount of time.

## B. Experiment subjects

We used two classes of experiment subjects. The first class consisted of real FSM specifications based on earlier industrial case studies. These FSMs can be found in the following repository: https://automata.cs.ru.nl/BenchmarkCircuits/Mealy. We picked this repository as it has been used in number of studies (see for example [75]. We used all minimal and strongly connected FSMs in this repository. Table I presents an overview of these FSMs. The second class of FSMs was synthetic FSMs derived using an existing tool used in many similar studies [40], [76], [77]. The synthetic FSMs were further classified according to the number of states (n), ranging from 10 to 200, increasing by 5, and number of inputs and outputs (i/o) ranging from 6 to 8 increasing by one. Each subclass contained 100 FSMs, so we used 11,700 synthetic FSMs during the experiments.

# C. Structure of the Experiments & visual encodings

1) Structure: Proposition 2 answered RQ1 negatively, i.e., checking the existence of bounded ordered W-sets is NP-hard. In order to answer RQs 2, 3 and 4, we compared the Bounded-Ordered W-Set generation algorithm (BOWA) with two baseline techniques: the classical W-Set generation algorithm (CWA), and the minimum W-Set generation algorithm (MWA) using different metrics pertaining to the respective research questions. The first metric relates to the quality dimension (RQ2), in which we compared algorithms based on the total number of inputs, total number of transfer inputs and total number of sequences for state identification. Next, we

investigated the algorithms' efficiency ( $\mathbb{RQ}3$ ): time and memory requirements. Finally, we evaluated the performances of the algorithms when generating a test suite with the W-method by measuring the total length of the test cases encompassing the generated sequences ( $\mathbb{RQ}4$ ).

The experiment begins by applying BOWA, MWA, and CWA to the experimental subjects. For each algorithm, we computed the SISs and SIPs using the *W*-sets and stored the total number of inputs and sequences in SISs and the total number of inputs for transfers. We provide the results in Sections VI-D1, VI-D2 and VI-D3, respectively. Moreover, we present the time and memory requirement while constructing the *W*-sets in Section VI-E. Finally, we used *W*-sets, SISs, and SIPs to compute TSs and stored the total number of inputs and sequences in TSs; the results are given in Section VI-F.

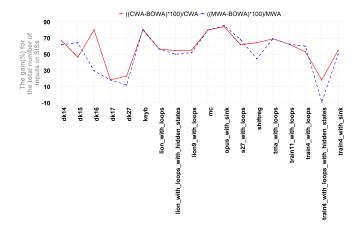

2) Visual encodings: To represent the results obtained from FSM systems modelling real systems, we used line and point charts, where the x-axis represents the FSM's name, and the y-axis represents the relative gain/loss (in percents) using the formula  $\frac{(a-b)*100}{a}$  for the metric. A similar technique is used to visualise the results for synthetic FSMs. The main difference is that since we have a larger population of subject systems and a larger variety, we could group the FSMs based on number of input/output (6,7 and 8) and number of states. We produced separate charts for the different numbers of input/output. In each chart, the x-axis represents the number of states, and the y-axis represents the relative gain/loss (in percentage).

### D. State Identification Costs

In this section, we analyse different metrics to answer **RQ2**, namely, whether using BO-WSets reduces the cost of state identification. To do so, we compare the total number of inputs (also referred to as the length of the state identification sequences), the number of sequences (also referred to as the number of reset operations), and the number of transfer inputs among the three algorithms.

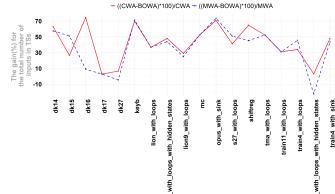

1) Total number of inputs (length) of state identification sequences: We start by answering **RQ2.1**, i.e., whether using BO-WSets reduces the total number of inputs (length) required to identify the states.

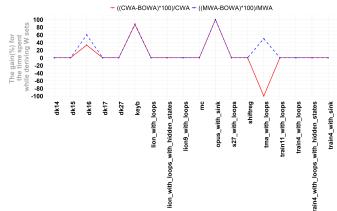

The results for FSMs modelling real systems are given in Figure 3a. To begin with, we observe that BOWA generates state identification sequences with fewer inputs except for one FSM (train4\_with\_loops\_with\_hidden\_states), where MWA produces state identification sequences with fewer inputs. For the other benchmark FSMs, BOWA generates state identification sequences containing 50% fewer inputs on average. In the best case, FSM opus\_with\_sink, our approach uses 88% fewer inputs. Moreover, we can claim that the total number of inputs of the SISs generated by the second baseline technique, CWA, is comparable to MWA except for FSMs dk16 and train4\_with\_loops\_with\_hidden\_states.

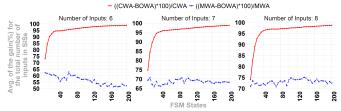

Figure 3b illustrates the averages of the total number of inputs of the SISs constructed for synthetic FSMs. When the number of inputs/outputs is 6, 7, and 8, on average, BOWA generates state identification sequences with 58%, 68%, and

(b) Average results obtained from synthetic FSMs

Fig. 3: The gains regarding the total number of inputs of state identification sequences.

74% fewer inputs than MWA, respectively. However, compared to CWA, BOWA generates state identification sequences having 95% fewer inputs on average, regardless of the number of inputs that the FSMs have. Finally, in Supplementary Table 1 we present how often BOWA leads to shorter state identification sequences. The results show that in all cases, BOWA generated state identification sequences with fewer inputs.

These results are consistent with our expectations; BOWA can reduce the number of inputs used during state identification. To further investigate the results, we applied the Wilcoxon Signed-Rank Test with a confidence interval of 95%, where the null hypothesis states that *the median difference between the paired observations is zero* (no significant difference). Wilcoxon test results obtained from BOWA and MWA confirm that the populations' medians are statistically different (minimum was p = 0.0000231 and maximum was p = 0.0019).

2) Number of sequences (resets) of state identification sequences: In this section, we address **RQ2.2**, i.e., whether using BO-WSets reduces the number of sequences (resets) required to identify the states.

In all experiments, whether performed on real-FSMS or synthetic FSMs, BOWA generated a single sequence, reducing the number of resets to one<sup>4</sup>. Therefore, these experiments show immense differences between BOWA and baseline algorithms.

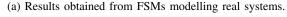

When analysing real FSMs (Figure 4a), we observe that the performances of CWA and MWA are comparable. Compared

(a) Results obtained from FSMs modelling real systems.

(b) Averages of the results obtained from synthetic FSMs.

Fig. 4: The gains regarding the total number of sequences in state identification sequences.

to these baseline approaches, BOWA leads to an average reduction in the total number of SISs (number of resets) of 95%. The maximum reduction is 99.99% in FSM keyb.

As expected, the results on the total number of SISs derived from synthetic FSMs also favour BOWA (Figure 4b). We see that, on average, BOWA requires 99.73% fewer resets than MWA (minimum is 98%, and maximum is 99.9%) and requires 99.99% fewer resets than CWA, on average. We also observe that the number of resets due to MWA is typically fewer than CWA, but it tends to converge to CWA as the number of states increases.

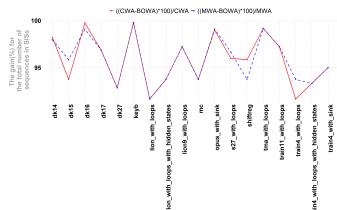

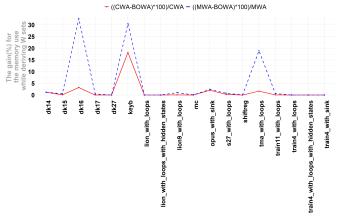

3) Number of transfer inputs: Finally, we consider **RQ2.3**, namely, whether using BO-WSets reduces the total number of transfer inputs (length) required to identify the states.

For the real FSMs (Figure 5a), we observe that using BOWA reduced the number of transfer inputs by 70% compared to CWA, on average (the maximum is 99.99%, the minimum is 49%). Moreover, we see that MWA performs slightly better than CWA, and this time BOWA reduced the number of inputs in transfer sequences by 53%, on average (the maximum is 99.99%, the minimum is 22%).

Figure 5b summarises the averages of the percentage-wise gain/loss regarding the number of transfer inputs during state identification for synthetic FSMs. The results confirm those gathered from real FSMs. On average, the BOWA algorithm generates 87% fewer transfer inputs for state identification than CWA, regardless of the input and output number (the maximum is 91%, the minimum is 80.5%). Moreover, in all test subjects, BOWA generated fewer transfer sequences (see Supplementary Table 1). When comparing BOWA and MWA,

<sup>&</sup>lt;sup>4</sup>Please see Supplementary Table 1

(b) Averages of the results obtained from synthetic FSMs.

Fig. 5: The gains regarding the total number of transfer inputs in state identification.

the average gain dropped to 59%, 63%, and 68% for 6,7, and 8 input/output values, respectively (the maximum is 76%, the minimum is 40%). We also noted that the gain increases with the number of states. Supplementary Table 1 shows that when the number of states is larger than 30, BOWA generates fewer sequences in all test subjects than the baseline approaches.

### E. Scalability

In this section, we address **RQ3**, i.e., the computation resources that we need to construct BO-WSets and how this demand differs from other state-of-the-art approaches.

To answer this question, we compared both the execution time and the memory requirements of our BOWA algorithm against the state-of-the-art CWA and MWA algorithms.

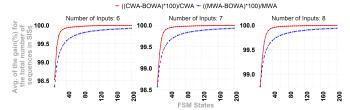

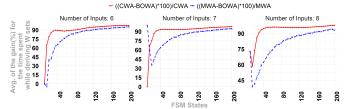

1) Time Requirements: We start by analysing the execution times to answer **RQ3.1**: How does the time required to construct BO-WSets differ from state-of-the-art approaches for deriving W-Sets?

The time requirements of algorithms while deriving W-sets from FSMs modelling real systems are given in Figure 6a. We observe that for real systems, which do not feature much variance in size and are all relatively small, the execution times of the baseline approaches (CWA and MWA) are similar. However, we also observe that the performance of BOWA varies across different FSM specifications. To investigate this, we used the Pearson correlation coefficient (PCC) analysis to investigate the factors that cause this variance. PCC analysis indicates that the number of states is the main factor impacting on the time (p-value: 0.00023) [74]. The cutoff value for the number of states that affects the computation time (using a

(a) Results obtained from FSMs modelling real systems.

(b) Averages of the results obtained from synthetic FSMs.

Fig. 6: The gains regarding the time requirements of algorithms while deriving *W*-Sets.

quantile 0.90) is n = 9. Based on these test subjects, we can claim that the BOWA algorithm will perform better if the number of states is larger than nine.

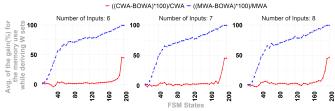

The differences are more pronounced for synthetic FSMs because they feature much more variety in size, and these FSMs feature many more states. We provide the average time the algorithms require to construct W-sets from synthetic FSMs in Figure 6b. These reinforce the results obtained from FSMs modelling real systems. On average, BOWA is 97% faster than CWA regardless of the number of inputs/outputs. Moreover, for all FSMs having more than 15 states, BOWA was faster than CWA (see Supplementary Table 1). However, on average, when n < 80 BOWA is 60%, 68.5% and 69% faster for 6, 7, and 8 inputs/outputs, respectively than MWA. Moreover, regardless of the input size, on average, BOWA is 95% faster than MWA when n > 80. The Supplementary Table 1 indicates that for all test subjects having more than 25 states BOWA was quicker. Considering the cost of sequences generated by BOWA, CWA and MWA (please see Section VI-D), these results are as expected: CWA generates many sequences, forcing it to spend more time, and MWA spends a significant amount of time to create compact W-sets, which require extra processing. On the other hand, BOWA generates a single W-set using simple heuristics.

2) Memory Requirements: In this section, we address **RQ3.2**, i.e., how the memory requirement for constructing BO-WSets differs from the state-of-the-art approaches for deriving W-Sets.

The results for real systems (Figure 7a) indicate that except for dk16, keyb and tma\_with\_loops the algorithms used

(a) Results obtained from FSMs modelling real systems.

(a) Results obtained from FSMs modelling real systems.

75

60

45

((CWA-BOWA)\*100)/CWA + ((MWA-BOWA)\*100)/MWA

Number of Inputs: 7

120

160 200

75

60

120 160

(b) Averages of the results obtained from synthetic FSMs.

Fig. 7: The gains regarding the memory requirements obtained from synthetic FSMs while deriving W-Sets.

a comparable amount of memory. However, for these three FSMs, BOWA needs 33%, 30.5%, and 17.5% less memory, respectively.

Figure 7b summarises the memory requirements for synthetic FSMs. The results suggest that, on average, BOWA requires 76% less memory than MWA (maximum of 99.99%; minimum of 0%) and Supplementary Table 1 indicates that BOWA needs less memory than MWA in all cases when n > 25. When compared to CWA, Figure 7b indicates that the average reduction is 23%, however, when n < 180, the memory requirements of the algorithms are comparable. We investigated this and performed a PCC analysis, which indicated that a threshold n = 180 for the variable "number of states" (using quantile 0.90) was statistically significant. So, for CWA, when the number of states exceeds this threshold, BOWA is expected to use less memory. However, when we inspect Supplementary Table 1, we observe that in most cases, BOWA needed less memory than CWA. These results indicate that concerning memory requirement, BOWA is as light-weight as CWA and can be more efficient when the number of states exceeds 180.

To assess these observations, we applied the Wilcoxon test [74], [78] using .95 significance level to check whether there is a statistically significant difference between the memory requirements across these three algorithms. As suspected, we reject the null hypothesis when analysing BOWA and MWA based on the p-value (max: 0.0064, min: 0.0055), which indicates statistical significance. Moreover, when comparing CWA and BOWA, we accept the null hypothesis for  $n \le 180$ as the minimum p-value is 0.062 and reject the null hypothesis when n > 180 as the maximum p-value was 0.000122.

(b) Averages of the results obtained from synthetic FSMs.

Fig. 8: The gains regarding the total number of inputs in TSs.

# F. Test Suite Costs

30 15

Number of Inputs: 6

120 160

Our last and final measurements concern the total cost of test suites in which the generated state identification sequences are embedded. Using these measurements, we aim to answer RQ4, namely, whether using BO-WSets reduces the cost of test suites.

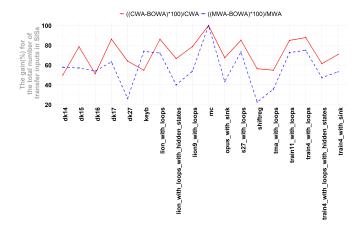

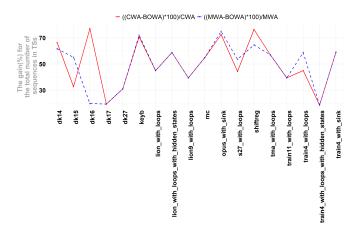

1) Total number of inputs (length) of test suites: We start by answering **RQ4.1**, i.e., whether using BO-WSets reduces the total number of inputs (length) in test suites.

In this section, we compare the performances of algorithms by considering the total number of inputs and sequences generated by the W-Method [5]. For CWA and MWA, we executed the W-Method using the W-sets produced by these algorithms as exemplified in Section III. For BOWA, we fed the W-Method with the SIPs constructed by Algorithm 2. However, we used the BO-WSETs produced by Algorithm 1 while generating transition verification sequences in the W-Method.

The total number of inputs (length) in tests using the W-Method generated from the FSMs modelling real systems are given in Figure 8a. Except for two FSMs (dk27, and train4\_with\_loops\_with\_hidden\_states), the W-Sets generated by the BOWA algorithm contain fewer inputs (maximum 80% reduction, on average 30% fewer inputs).

Figure 8b shows the average number of inputs in tests derived from synthetic FSMs. When comparing BOWA against MWA, we observe that on average i) 15% reduction in the number of inputs when there are 6 input/output, ii) 40% reduction in the number of inputs when there are 7 input/output, and iii) 48% reduction in the number of inputs when there are 8 input/output. However, we also observed that the reduction gradually reduces as the number of states increases.

When we inspect the number of test subjects for which BOWA leads to shorter test suites (Supplementary Table 1), we observe that as the number of inputs/outputs increases, BOWA starts performing better than MWA (there are only three FSMs with eight inputs and outputs for which MWA was better than BOWA). However, when the number of inputs and outputs reduces, MWA performs better and this is more evident when inputs/outputs is six. This is probably due to the impact of the test sequences used for the transition verification phase of the test suites. It is important to note that MWA is an optimisation algorithm focusing on deriving compact *W*-sets. So, as the number of states increases, this impact becomes more visible. However, we also note that in all computations, this reduction tends to evolve into a plateau, suggesting that the advantage of MWA is limited compared to the BOWA.

As expected, BOWA leads to test suites having fewer inputs (92% on average) compared to CWA<sup>5</sup>. To investigate our findings, we applied the Wilcoxon test to the results. For all n and input/output values, we observed that the p value was below 0.05, indicating statistical significance.

2) Number of sequences (resets) in test suites: We now address our last research question **RQ4.2**, i.e., whether using BO-WSets reduces the number of sequences (resets) in test suites.

The total number of sequences in TSs generated for FSMs modelling real systems are given in Figure 9a. We observe that, the performances of MWA and CWA are similar, with the largest difference being found with FSM dk16. However, overall, the tests constructed using the BOWA algorithm have fewer sequences. The maximum is 83% fewer sequences (shiftreg), the minimum is 22.3% fewer sequences (dk16, dk17, and train4\_with\_loops\_with\_hidden\_states).

Similar results can be observed with synthetic FSMs (Figure 9b). Compared to MWA, the reduction in the number of test sequences in TSs is 39%, 54%, and 56% on average when the number of inputs/outputs is 6, 7 and 8, respectively. Similar to the results we obtain in Section VI-F1, the percentagewise gain due to BOWA tends to reduce as the number of states increases. However, interestingly, the Supplementary table 1 indicates that in the majority of the cases, BOWA leads to fewer sequences in TSs, which indicates that there are relatively few cases for which MWA leads to fewer sequences in TSs and the difference between MWA and BOWA is high. Again, we relate this reduction to the impact of the transition verification phase, as described above. In comparison with CWA, the reduction is 94% on average regardless of the number of inputs/outputs.

We applied the Wilcoxon test to verify the difference. The results indicate that the distributions of the number of sequences in the tests constructed by BOWA and MWA are statistically different (the maximum was p = 0.000378163, the minimum was p = 0.0001464).

(a) Results obtained from FSMs modelling real systems.

(b) The averages of the results obtained from synthetic FSMs.

Fig. 9: The gains regarding the total number of sequences in TSs.

# VII. THREATS TO VALIDITY

The major external threat to the validity of our work is generalisability. To address this, we not only used synthetic FSMs but also used FSMs modelling real systems.

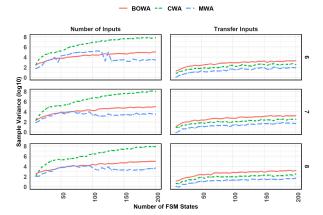

With respect to internal validity, the primary concern is the selection of synthetic FSMs: they may have common transition structure reducing the variety of the test subjects. To minimise this threat, we used a framework previously used in several works ( [40], [77], [79]–[81]) to generate synthetic FSMs. In Figure 10, we provided the average sample variance of the results obtained from synthetic FSMs for different metrics with varying input/output values. The charts in the first row are for FSMs with 6 input/output symbols, the second row is for FSMs with 7 input/output symbols and the last row is for FSMs with 8 input/output symbols. The *y*-axis is given in log<sub>10</sub> scale.